# 2 x 50 µm Ultra Low Noise InP pHEMT

The pH-100 series of discrete ultra low noise InP HEMT transistors come in various standard sizes ranging from 50µm to 400µm total gate width. All transistors are DC-tested before shipment and have a unique label to allow for full traceability. In general it is best to use smaller devices at higher frequencies and larger devices at lower frequencies. Applications at room temperature often benefit from devices with more but shorter fingers, whereas 2-finger devices are usually optimal for applications at cryogenic temperatures.

The pH-100-2F50 with 100um total gate width is typically used for hybrid LNAs covering frequency ranges from Ku-band up to Ka-band. Use in other frequency bands is possible and may make sense in cases with special requirements.

### **Basic Characteristics**

| Temperature                                     | 300 K      |

|-------------------------------------------------|------------|

| Transconductance gm                             | 1250 mS/mm |

| Maximum Drain Current I <sub>DSmax</sub>        | 800 mA/mm  |

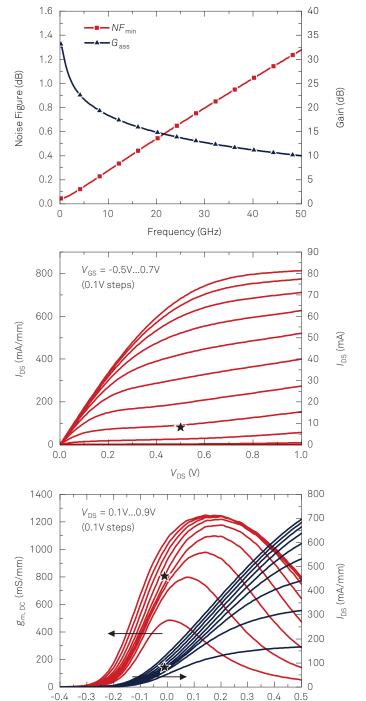

| Noise Figure NF <sub>min</sub> (@4 GHz)         | 0.12 dB    |

| Noise Temperature T <sub>min</sub> (@4 GHz)     | 8 K        |

| Associated Gain (@4 GHz)                        | 22.8 dB    |

| Noise Figure <i>NF</i> <sub>min</sub> (@30 GHz) | 0.80 dB    |

| Noise Temperature $T_{\rm min}$ (@30 GHz)       | 58 K       |

| Associated Gain (@30 GHz)                       | 12.7 dB    |

## Typical Bias Range

#### **Maximum Ratings** $V_{DS} = 1.5 \text{ V}$ $V_{DS} = 0.2 \text{ V} \dots 0.75 \text{ V}$ $I_{DS} = 20 \text{ mA/mm} \dots 400 \text{ mA/mm}$ $V_{GD} = -2.5 \text{ V} \dots 0.5 \text{ V}$ (2 mA ... 40 mA) $V_{GS} = -1.0 \text{ V} \dots 0.9 \text{ V}$

### **Die Attach Notes**

$V_{GS} = -0.2 \text{ V} \dots 0.25 \text{ V}$

- Maximum die attach temperature is 200 °C

- · It is recommended to use conductive epoxy

- Gold bond wires with diameter of ≤ 25 µm are recommended

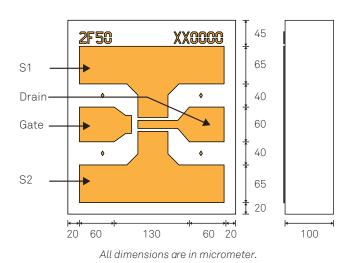

- Both source pads (S1, S2) need to be grounded

- To prevent damage to the active area in the center of the die avoid contact to this area during handling

$\bigstar$  denotes the typical low noise bias point of  $V_{ns}$  = 0.5 V and  $I_{ps} = 80 \text{mA/mm}$  (8 mA). The noise figure and gain plot is given for this bias and was obtained from on-wafer measurements. Data and models are available on request.

$V_{\rm GS}\left(V\right)$